### DIGITAL SYSTEMS DESIGN (ECEN 2202)

**Time Allotted : 3 hrs**

Full Marks: 70

Figures out of the right margin indicate full marks.

Candidates are required to answer Group A and <u>any 5 (five)</u> from Group B to E, taking <u>at least one</u> from each group.

Candidates are required to give answer in their own words as far as practicable.

# Group – A (Multiple Choice Type Questions)

| 1. | Choos  | wing: 10 × 1 = 10                                                                    |                                                                          |

|----|--------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|    | (i)    | What are the basic gates in MOS logic fam<br>(a) NAND and NOR<br>(c) NAND and OR     | ily?<br>(b) AND and OR<br>(d) AND and NOR.                               |

|    | (ii)   | A modulus -10 Johnson counter requires a<br>(a) 10 flip-flops<br>(c) 4 flip-flops    | minimum of<br>(b) 5 flip-flops<br>(d) 12 flip-flops.                     |

|    | (iii)  | The Excess-3 code is a<br>(a) cyclic code<br>(c) self-complementing code             | <ul><li>(b) weighted code</li><li>(d) error correcting code.</li></ul>   |

|    | (iv)   | A mod-2 counter, followed by a mod-5 cou<br>(a) decade counter<br>(c) mod-11 counter | inter is<br>(b) mod-9 counter<br>(d) mod-7 counter.                      |

|    | (v)    | The memory which is ultraviolet erasable<br>(a) RAM<br>(c) PROM                      | and electrically programmable is<br>(b) EEROM<br>(d) EPROM.              |

|    | (vi)   | The fastest logic gate family is<br>(a) CMOS<br>(c) TTL                              | (b) ECL<br>(d) RTL.                                                      |

|    | (vii)  | An example of reflected code is<br>(a) BCD<br>(c) GRAY                               | (b) ASCII<br>(d) Hamming.                                                |

|    | (viii) | What will be the output from a D flip – flog<br>(a) 0<br>(c) No change               | p if the clock is low and D = 0?<br>(b) 1<br>(d) Toggle between 0 and 1. |

|    |        |                                                                                      |                                                                          |

ECEN 2202

- (ix) Which of the following gives the correct number of multiplexers required to build a 32 × 1 multiplexer?

(a) Two 16 × 1 mux

(b) Three 8 × 1 mux

(c) Two 8 × 1 mux

(d) Three 16 × 1 mux.

- (x) Active devices used in digital circuit s generally operates as

(a) Amplifier

(b) Switches

(c) Rectifier

(d) waveform generator.

## Group - B

#### 2. (a) Represent

- (i) (4578)<sub>10</sub> in Gray code

- (ii)  $(572.61)_8$  in common binary code

- (iii) Realize Y = (AB)' + A + (B+C)' using NAND gates only.

(b) If the solutions of the equation x<sup>2</sup>-11x+22=0 are x=3, 6 then determine the base of the numbers.

[C01/Evaluate/HOCQ]

- (3+3+3)+3=12

- 3. (a)Simplify the given Boolean expression using Quine-McCluskey procedure<br/> $f(A,B,C,D) = \sum m(1,4,6,7,8,9,10,11,15);$ [CO1/Apply/IOCQ](b)Realize a Half-Subtractor using NAND gates only.[CO2/Apply/IOCQ]8 + 4 = 12

# Group - C

4. (a) Realize a full adder circuit using half adder and necessary logic gates.

[(CO2)(Remember/LOCQ)]

(b) Design a BCD adder that will add two 4 bit BCD numbers. [(CO2)(Analyze/HOCQ)]

6 + 6 = 12

5. (a) Construct a *8:1* line multiplexer using 2:1 line multiplexers only.

(b) Implement the function  $f(A,B,C,D) = \sum m (0,1,2,4,6,9,10,12,14)$  using a 4:1 line Multiplexer. [CO2/Evaluate/HOCQ]

6 + 6 = 12

# Group - D

6. (a) What is the advantage of J-K Flip-flop over S-R flip-flop?

[(CO3)(Remember/LOCQ)]

(b) Write the truth table, state table, excitation table and hence derive the characteristics equation of SR flip-flop. [(CO3)(Analyze/HOCQ)]

(c) Realize J-K flip-flop using S-R flip-flop.

[(CO3)(Analyze/HOCQ)] 2 + 6 + 4 = 12

7. (a) Design a synchronous MOD 3 UP/DOWN Counter using D flip-flops.

[CO3/Create/HOCQ]

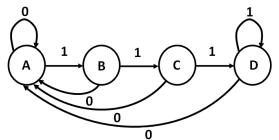

(b) A clocked sequential circuit has four states A, B, C & D as show in the state diagram of Fig.1. Assume state assignments as A = 00, B = 01, C = 10 and D = 11. Prepare the state table and draw circuit using D flip-flops.

[CO3/Evaluate/HOCQ]

Fig. 1: State diagram of a clocked sequential circuit

6 + 6 = 12

# Group - E

- 8. (a) Explain the operation of a successive approximation ADC with proper circuit diagram. [(CO4)(Remember/LOCQ)]

- (b) Explain the operation of a 4-bit R-2R ladder type DAC with proper circuit diagram. [(CO4)(Understand/LOCQ)]

- (c) What is the advantage of this type of DAC over counter type DAC? [(CO4)(Analyse/IOCQ)]

5 + 5 + 2 = 12

9. (a) Design a basic 2 input TTL NAND gate and explain.

[(CO5)(Remember/IOCQ)]

(b) Explain the operation of a 3 bit twisted ring counter.

[(CO3)(Understand/LOCQ)]

6 + 6 = 12

| Cognition Level         | LOCQ | IOCQ  | HOCQ  |

|-------------------------|------|-------|-------|

| Percentage distribution | 25   | 27.08 | 47.92 |

### **Course Outcome (CO):**

After the completion of the course students will be able to

- 1. Make use of the concept of Boolean algebra to minimize logic expressions by the algebraic method, K-map method, and Tabular method.

- 2. Construct different Combinational circuits like Adder, Subtractor, Multiplexer, De-Multiplexer, Decoder, Encoder, etc.

- 3. Design various types of Registers and Counters Circuits using Flip-Flops (Synchronous, Asynchronous, Irregular, Cascaded, Ring, Johnson).

- 4. Outline the concept of different types of A/D and D/A conversion techniques.

- 5. Realize basic gates using RTL, DTL, TTL, ECL, and CMOS logic families.

- 6. Relate the concept of Flip flops to analyze different memory systems including RAM, ROM, EPROM, EEROM, etc.

\*LOCQ: Lower Order Cognitive Question; IOCQ: Intermediate Order Cognitive Question; HOCQ: Higher Order Cognitive Question