M.TECH/AEIE/1st SEM/AEIE 5101/2017

- 7. (a) Obtain the expression for noise margin high  $(NM_H)$  for a CMOS inverter from the voltage transfer characteristics.

- (b) State how the Wilson MOS mirror can be modified to avoid the systematic current error. Derive an expression for output resistance in a Wilson MOS mirror.

Group - E

- 8 (a) Derive an expression for propagation delay in a CMOS inverter with capacitor load. Comment on the relation between propagation delay and capacitance of the load.

- (b) Draw the CMOS realization to implement the following logic expression,  $y = \overline{A(B + CD)}$

6 + 6 = 12

7 + (2 + 3) = 12

- 9 (a) Derive the expression for noise margin high from voltage transfer characteristics of a pseudo-NMOS inverter.

- (b) Explain with detailed circuit diagram for a process of writing '0' in a 6T SRAM cell.

6 + 6 = 12

#### M.TECH/AEIE/1st SEM/AEIE 5101/2017

# MICRO ELECTRONIC DEVICES AND CIRCUITS (AEIE 5101)

Time Allotted: 3 hrs

Full Marks: 70

Figures out of the right margin indicate full marks.

Candidates are required to answer Group A and <u>Any 5 (five)</u> from Group B to E, taking <u>at least one</u> from each group.

Candidates are required to give answer in their own words as far as practicable.

# Group – A (Multiple Choice Type Questions)

1. Choose the correct alternative for the following:

$10 \times 1 = 10$

- (i) The threshold voltage of an n-channel MOSFET can be increased by

(a) increasing the channel dopant concentration

(b) reducing the channel dopant concentration

(c) reducing gate oxide thickness

(d) reducing the channel length.

- (ii) In a CMOS inverter the upper MOSFET is

(a) active load

(b) passive load

(c) complementary load

(d) none of the above.

- (iii) What is the difference voltage output from an Op-Amp if the inputs are an ideal in-phase signal?(a) The differential gain times twice the input signal

- (b) The differential gain times the input signal

- (c) The common-mode gain times twice the input signal

(d) The common-mode gain times the input signal.

- (iv) The primary function of the bias circuit is to (a) hold the circuit stable at  $V_{CC}$

- (b) hold the circuit stable at  $V_{in}$

- (c) ensure proper gain is achieved

- (d) hold the circuit stable at the designed Q-point.

- (v) What is the voltage gain of the unity follower?

(a) 0

(b) 1

(c) -1

(d) infinity.

AEIE 5101

### M.TECH/AEIE/1st SEM/AEIE 5101/2017

(c) inductor

(vi) A MOSFET is

| (a) a current-controlled device | (b) a voltage-controlled device |

|---------------------------------|---------------------------------|

| (c) always forward-biased       | (d) reversed biased.            |

(vii) Which components are hard to fabricate into ICs? (a) diode

(b) resistor

(d) transistor.

- (viii) What is the most common method used for the growth of single crystals for IC fabrication? (a) epitaxial growth (b) czochralsky pulling technique

- (c) film deposition

(d) photolithography.

- (ix) Voltage follower is a special case of (a) inverting configuration (b) non-inverting configuration (d) integrator configuration.

- (c) difference configuration

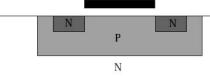

- (x)The MOSFET below

**AEIE 5101**

is labeled with the different types of silicon. The device is best described as

(a) an n-MOSFET in an N-well (c) a p-MOSFET in an N-well

(b) an n-MOSFET in a P-well (d) a p-MOSFET in a P-well.

Group - B

- 2. (a) What are the various steps involved in IC fabrication process? Briefly describe each step.

- Design an active resistor by using an n-channel MOSFET and derive (b) the expression for resistance.

5 + 7 = 12

- 3. (a) Derive the expression for current transfer ratio in a two transistor BJT Widlar current source.

- For  $I_{ref} = 1$  mA, find  $I_0$  when  $V_0 = 5V$ . For a cascade MOS mirror utilizing (b) devices with  $V_t = 0.5V$ ,  $\mu_n C_{ox} = 387 \mu A/V^2$ ,  $V_a' = 5V/\mu m$ ,  $W/L = 3.6 \mu m/0.36 \mu m$ and  $I_{ref}$  = 100 µA, find output resistance of the MOS mirror. 6 + 6 = 12

2

M.TECH/AEIE/1st SEM/AEIE 5101/2017

### Group - C

- An active-loaded MOS differential amplifier inside 741 Op-Amp has the fol 4. (a) specification:  $(W/L)_n = 100$ ,  $(W/L)_P = 200$ ,  $\mu_n C_{ox} = 2\mu_n C_{ox} = 0.2$  $V_{An} = |V_{Ap}| = 20 \text{ V}, \text{ I} = 0.8 \text{ mA}, \text{R}_{SS} = 25 \text{ k}\Omega.$  Calculate G<sub>M</sub>, Ad, |A<sub>CM</sub>| and CMRF MOS differential pair.

- (b) Deduce the expression for the transconductance for the input st a 741 Op-Amp.

7 + 5

- 5. (a) Derive the expression for output resistance in a 741 Op-Amp fro small signal model of the output stage.

- (b) Derive the relationship between unity-gain bandwidth  $(f_t)$  and rate (SR) in case of a 741 Op-Amp.

9+3

## Group - D

- Derive the expression for CMRR of an active loaded MOS differ 6. (a) pair.

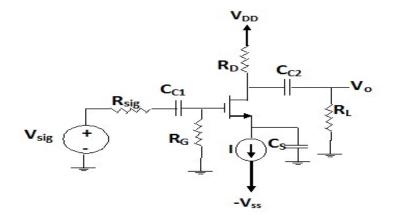

- Perform small signal analysis on the given NMOS amplifier c (b) shown in following figure. Find an expression for output impe and voltage gain.

**AEIE 5101**

3