## B.TECH/ECE/6<sup>TH</sup> SEM/ECEN 3201/2025

## DIGITAL VLSI DESIGN (ECEN 3201)

Time Allotted: 2½ hrs Full Marks: 60

Figures out of the right margin indicate full marks.

Candidates are required to answer Group A and any 4 (four) from Group B to E, taking one from each group.

Candidates are required to give answer in their own words as far as practicable.

1.

|        | Group                                                                                                                                                                                                                                   | - A                                                   |                                                                                           |                         |             |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------|-------------|

| Answ   | er any twelve:                                                                                                                                                                                                                          |                                                       |                                                                                           |                         | 12 × 1 = 12 |

|        | Choose the correct altern                                                                                                                                                                                                               | ative j                                               | for the follow                                                                            | wing                    |             |

| (i)    | NMOS passes (a) Strong '0' and weak '1' (c) Both strong '0' and '1'                                                                                                                                                                     | (b) Strong '1' and weak '0' (d) Both Weak '0' and '1' |                                                                                           |                         |             |

| (ii)   | Which of the following is true for a NMOS (a) $V_{DS}$ < ( $V_{GS}$ - $V_t$ ) (c) $V_{GS}$ < $V_t$                                                                                                                                      |                                                       | operating in the linear region?<br>(b) $V_{DS}$ > ( $V_{GS}$ - $V_t$ )<br>(d) $V_{GS}$ =0 |                         | ion?        |

| (iii)  | Industry Standard SRAM Bit-Cell has (a) 2 (b) 4                                                                                                                                                                                         | s Belo<br>(c) 6                                       | w Number                                                                                  | of Transistors<br>(d) 8 |             |

| (iv)   | Which of the following statement is not true for SRAM?  (a) It does not require periodic refreshing  (b) It is made up of six CMOS transistors  (c) It has low capacity but offers high speed  (d) It stores data in the form of charge |                                                       |                                                                                           |                         |             |

| (v)    | The actual storage element in DRAM (a) Diode (b) Capacitor                                                                                                                                                                              |                                                       | osfet                                                                                     | (d) Flip flop           |             |

| (vi)   | Verilog is<br>(a) Machine Language<br>(c) Hardware Description Language                                                                                                                                                                 |                                                       | (b) Assembly Level Language<br>(d) Software Programming Language                          |                         |             |

| (vii)  | Control and Data Flow Graph is related to (a) Floorplan (c) High Level Synthesis                                                                                                                                                        |                                                       | (b) Logic Synthesis<br>(d) Routing                                                        |                         |             |

| (viii) | What are the advantages of design rules? (a) durable (c) portable                                                                                                                                                                       |                                                       | <ul><li>(b) scalable</li><li>(d) all of the above</li></ul>                               |                         |             |

| (ix)   | Bridging Fault Occurs when (a) Signal Gets shorted to Vdd (b) Signal Gets shorted to Vss (c) One Signal Gets shorted to another Signal (d) CLK Signal Gets Shorted to Vdd                                                                       |  |  |  |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| (x)    | Stuck-at-1 fault happens when output of a Gate is  (a) shorted to VSS  (b) shorted to another signal  (c) shorted to VDD  (d) becomes floating                                                                                                  |  |  |  |  |

|        | Fill in the blanks with the correct word                                                                                                                                                                                                        |  |  |  |  |

| (xi)   | Full Form of TTM is                                                                                                                                                                                                                             |  |  |  |  |

| (xii)  | Dynamic Gate followed by Static Gate Pair is Called                                                                                                                                                                                             |  |  |  |  |

| (xiii) | The full form of RTL is                                                                                                                                                                                                                         |  |  |  |  |

| (xiv)  | The number of transistors needed to implement F=(AB+CDE)' is                                                                                                                                                                                    |  |  |  |  |

| (xv)   | The process by which impurities are added to the pure form of Silicon is called                                                                                                                                                                 |  |  |  |  |

|        | Group - B                                                                                                                                                                                                                                       |  |  |  |  |

| (a)    | A 64-bit off-chip bus operating at 1 V and 100 MHz clock rate is driving 25 pF/bit capacitance. Each bit is estimated to have a toggling probability of 0.25 at each clock cycle. Calculate the dynamic power dissipation in operating the bus. |  |  |  |  |

| (b)    | Design a CMOS gate for the logic function $f(a,b,c)=\Sigma m(0,1,3,5,7)$ . Mention the widths of NMOS and PMOS for the above design so that the current driving capability remains same as that of the basic CMOS inverter. [(CO1)(Apply/IOCQ)] |  |  |  |  |

| (c)    | Mention the differences between a full custom and a semi custom design of VIsi circuits. $[(CO1)(Remember/LOCQ)]$ $\mathbf{4+6+2=12}$                                                                                                           |  |  |  |  |

| (a)    | Differentiate between pseudo NMOS logic and CMOS logic in terms of their advantages and disadvantages along with circuit examples. [(CO2,CO3)(Analyse/HOCQ)]                                                                                    |  |  |  |  |

| (b)    | Briefly describe the different regions of operation of NMOS and PMOS in CMOS inverter circuit using VTC upon changing the input voltage of the inverter.  [(CO4)(Remember/LOCQ)] $6 + 6 = 12$                                                   |  |  |  |  |

|        | Group - C                                                                                                                                                                                                                                       |  |  |  |  |

2.

3.

4. (a) Design a static CMOS circuit of a 3-input NAND gate and construct its layout using Euler Path Algorithm. [(CO4)(Apply/IOCQ)]

(b) Explain the Write-1 operation of a 6-Transistor SRAM cell with the help of the circuit diagram. [(CO4)(Understand/LOCQ)]

7 + 5 = 12

(a) 5. Show the CMOS implementation of a clocked S-R latch. Mention whether the circuit is edge triggered or level triggered using timing diagram.

[(CO3)(Analyse/HOCQ)]

(b) Draw the stick diagram of a two-input NOR gate. [(CO4)(Apply/IOCQ)]

7 + 5 = 12

## Group - D

- Implement a 3:8 decoder using Verilog code. 6. (a) [(CO5)(Understand/LOCQ)]

- Write the Verilog code for the structural modelling of a 8:1 multiplexer using (b) three 2:1 multiplexer modules. Draw the complete block diagram of the model.

[(CO5)(Remember/LOCQ)]

6 + 6 = 12

Implement Verilog Coding for 2:1 Multiplexor using Data Flow Model. 7. (a)

[(CO5)(Apply/IOCQ)]

- Implement Verilog Coding for Rising Edge Triggered D-Flip Flop using (b) Behavioural Model. [(CO5)(Apply/IOCQ)]

- Using Verilog Coding Example Explain Structural Modeling. (c) [(CO5)(Apply/IOCQ)]

4 + 4 + 4 = 12

## Group - E

- Write short notes on (i) floor planning (ii) routing. 8. (a) [(CO6)(Remember/LOCQ)]

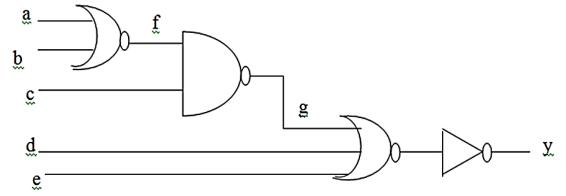

- Find the test vector for the following circuit which has got a Stuck-at-0 fault at 'g' (b)

[(CO6)(Evaluate/HOCQ)]

5 + 7 = 12

- Realise a logic function F=(AB+C)' using CMOS logic and mention the input test 9. (a) vectors if

- (i) one of the NMOS transistors in PDN is stuck open.

(ii) one of the PMOS transistors in PUN is stuck short.

[(CO6)(Analyse/HOCQ)]

What are the 3 types of Delay Faults? Briefly state the nature of these faults. (b)

[(CO6)(Remember/LOCQ)]

6 + 6 = 12

| Cognition Level         | LOCQ | IOCQ  | HOCQ  |

|-------------------------|------|-------|-------|

| Percentage distribution | 37.5 | 31.25 | 31.25 |